在对片上电源的早期研究中,研究人员已经证明薄膜微电容器可以在半导体芯片上制造。

曾经位于微处理器外部的大部分内容都已被集成。当今的芯片具有模数转换器 (ADC)、数模转换器 (DAC)、电容式触摸输入、比较器以及许多其他内置外设。有些芯片甚至配备了小型现场可编程门阵列 (FPGA) ) 部分。然而,电源仍然始终是外部的。

这种情况可能很快就会改变。劳伦斯伯克利国家实验室(伯克利实验室)和加州大学伯克利分校的科学家开发了一种薄膜存储电容器,可以直接在微处理器之上制造。

由于许多现代微控制器的功耗要求极低,这种新原型可能会导致设备无需外部电源即可运行。

为什么硅电容器如此困难?

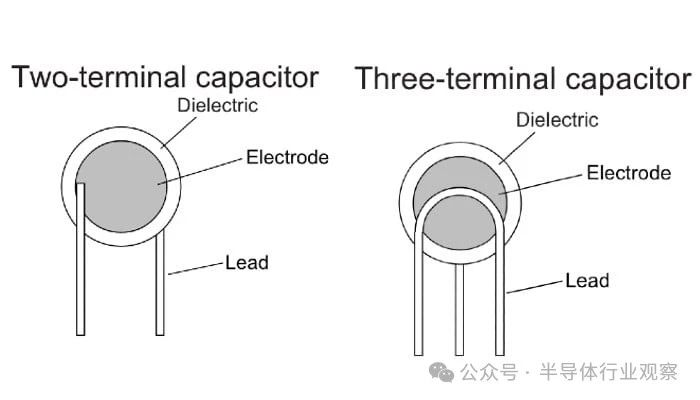

电容器通过静电电荷存储能量。这与电池不同,电池通过分子化学结构利用电子运动。标准电容器由两个导电金属层构成,两个导电金属层被称为电介质的绝缘层隔开。电介质可以是任何绝缘材料,包括空气。厚度和物理尺寸以及电介质的其他特性决定了电容器存储电荷的能力。

电容器简单的三层结构使其成为比复杂的电化学电池更有吸引力的蓄电设备。电容器还具有长寿命、无化学泄漏风险以及快速充电/放电能力。

集成电路通常没有内置电容器,DRAM 单元是少数例外之一。电容器所需的空间量令人望而却步。虽然集成这些设备并不困难,但资源昂贵。电容器的功率尺寸比使得将电容器放置在 IC 内部即使不是不可能,也具有挑战性。硅电容器在 DRAM 单元中工作,因为能量存储要求非常低,并且 DRAM 刷新周期提供定期维护电力。

负电容的救援

伯克利实验室的科学家们一直在研究负电容材料,以降低 MOSFET 晶体管的阈值电压。他们发现,相对于能量存储,在传统电介质层顶部放置一层负电容电介质会增加电容。虽然两层传统电介质会降低电容,但一层负电介质层和一层传统电介质层具有相反的效果。

对于正电容,增加电压会增加电容器中的电荷。对于负电容,电荷的变化会导致电压沿相反方向变化。电压下降会增加电荷。这种效应有点类似于电感器中磁场崩溃所产生的电荷。

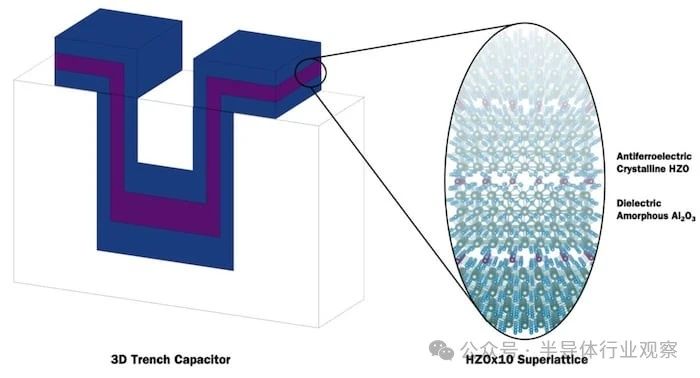

负电容电介质由二氧化铪和二氧化锆(HfO2 -ZrO2或HZO)组成 ,称为反铁电薄膜。HfO2和ZrO2的混合物使用原子层沉积直接在硅上生长,该工艺目前在芯片制造行业中很常见。

原型机的储能密度

该团队通过他们的研究设备发现了创纪录的高能量存储密度(ESD)和功率密度(PD)。ESD一部分来自材料,一部分来自建筑架构。HZO 电容器在纵横比高达 100:1 的深 3D 沟槽中生长为分层薄膜。该结构的灵感来自 DRAM 电容器,也使用深 3D 沟槽。

与传统静电电容器相比,该微电容器具有创纪录的能量密度。芯片内帽的能量密度为80 mJ-cm-2 (9x),功率密度为300 kW-cm-2 (170x)。

物联网芯片集成电容器

研究人员的最终目标是制造不需要外部电力存储的低功耗硅芯片。许多小型系统,例如远程传感器和物联网设备,大部分时间都处于深度睡眠模式,只需要短时间的供电。电容器非常适合此类应用。

虽然芯片集成电容器可能不具备较大的传统电池或大型外部电容器的总能量容量,但它可以快速提供电力,满足许多远程边缘计算代理的短突发模式电力要求。

它直接集成到硅中显着降低了传输和转换损耗。将超低功耗硅与片上电源相结合,有可能创造出比当今更小尺寸和更低成本的新型远程设备。

免责声明:来源标记为网络的文章其原创性及文中陈述文字和内容未经我司证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺请读者仅作参考并请自行核实相关内容,版权归原作者所有,如有侵权请联系我们删除。